# Perfect 4-element Match

Gord Rabjohn 2019-2024

#### Matching

- Matching networks can transform one impedance to another.

- A simple 2-element network does this perfectly only at one frequency.

- A 4-element network (series-shunt-series-shunt ladder network) can provide a perfect match at 2 frequencies. If these frequencies are selected carefully, a good match over a reasonable bandwidth can be achieved.

#### Overview

- Here, I demonstrate a parameterized match that results in a *perfect* two-null impedance transformation.

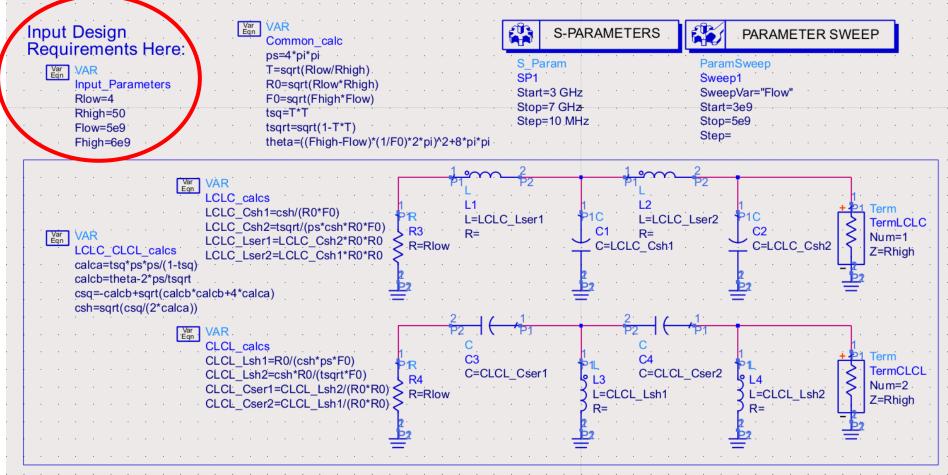

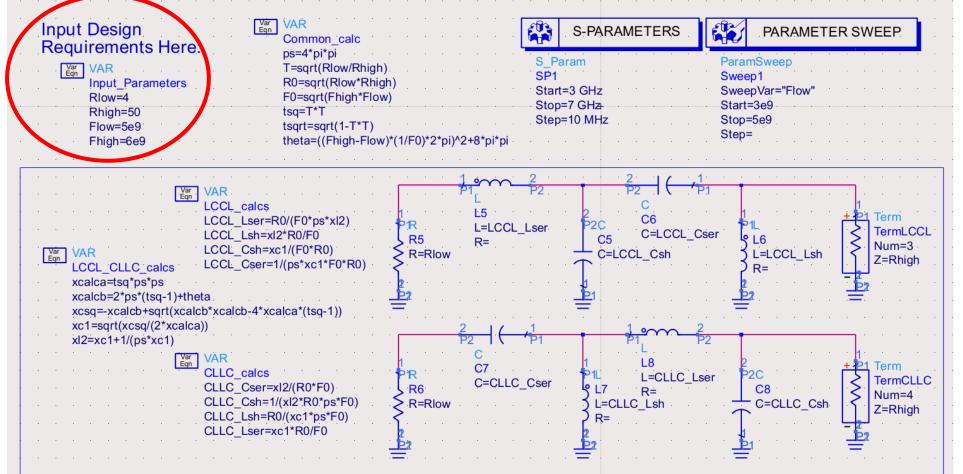

- You supply the desired frequency range and input and output resistances.

- It provides a 4-element circuit that does a two-null "bow-tie" match (with perfect match at the two nulls), with the nulls symmetrically placed.

- It is an exact solution. It is also a unique solution (there is only one combination of elements (in a given topology) that will result in the perfect match).

- It works for all frequencies and all termination impedances.

- Works for 4 different design prototypes.

- I used ADS, but the technique can be used in any microwave simulator.

#### Usage

- You specify:

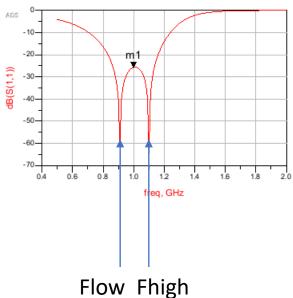

- Flow, Fhigh, (the frequencies at which the return loss nulls occur, generally a bit inside the required band of operation).

- Rlow, Rhigh, (the resistances that match input and output, in other words, if Rlow is present at the input, the output will look close to Rhigh over the band of operation).

- The closed-form equations generate the L and C values required for 4 different network topologies.

- You can use Flow, Fhigh, Rlow, Rhigh (or combinations of these, like Fo, Ro) with the ADS optimizer, or in tune mode.

- Implemented in equations in ADS, and in a spread-sheet.

- Select the topology with the most convenient component values.

## What you will get

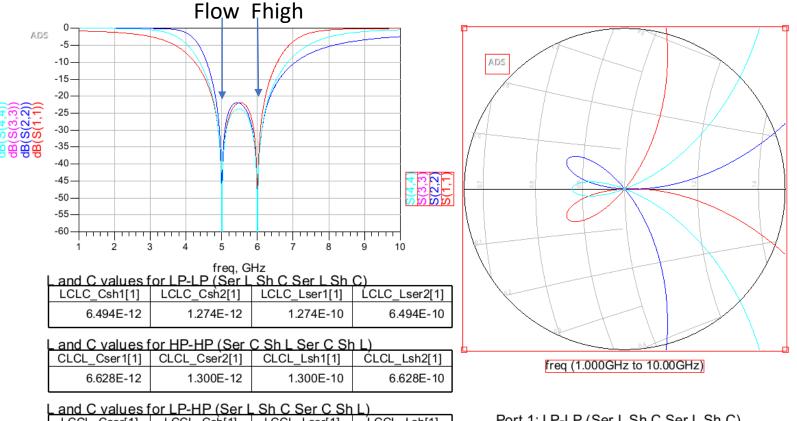

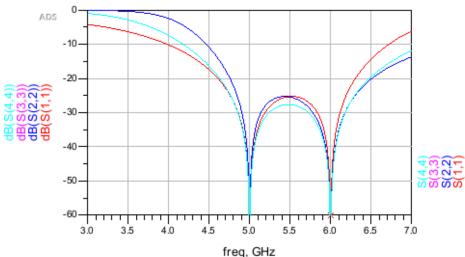

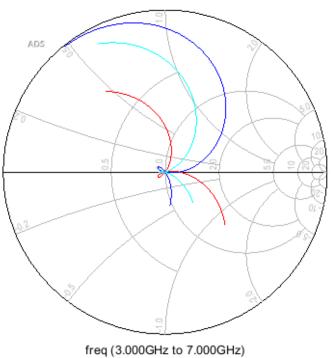

• You will get a match like this (shown for all 4 topologies): (this was 2 ohms to 50 ohms)

| LCCL_Cser[1] | LCCL_Csh[1] | LCCL_Lser[1] | LCCL_Lsh[1] |

|--------------|-------------|--------------|-------------|

| 1.514E-12    | 5.577E-12   | 1.191E-10    | 7.091E-10   |

#### Port 1: LP-LP (Ser L Sh C Ser L Sh C) Port 2: HP-HP (Ser C Sh L Ser C Sh L) Port 3: LP-HP (Ser L Sh C Ser C Sh L) Port 4: HP-LP (Ser C Sh L Ser L Sh C) Port 5: Transformer (Ser C XFMR Sh C)

#### and C values for UD ID (Sar C Sh I Sar I Sh C)

| ł | CLLC Cser[1] | CLLC Csh[1] | CLLC Lser[1] | CLLC Lsh[1] |

|---|--------------|-------------|--------------|-------------|

|   | 7.091E-12    | 1.191E-12   | 5.577E-10    | 1.514E-10   |

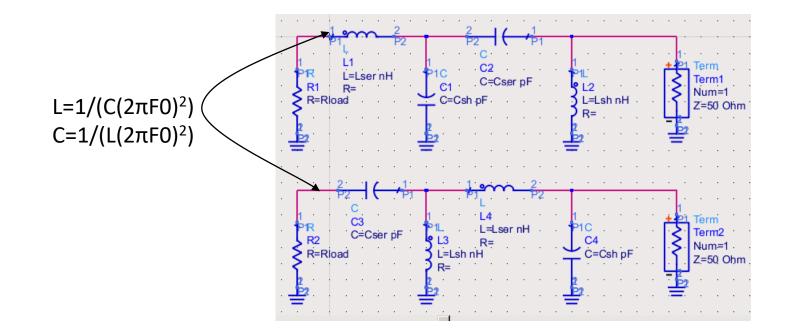

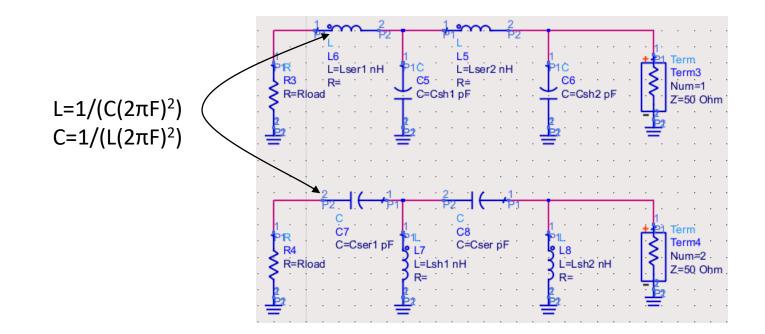

#### ADS: LPLP and HPHP circuits

You need 4 VAR blocks: Input\_Parameters, Common\_calc, LCLC\_CLCL\_calcs, and either CLCL\_calcs or LCLC\_calcs

#### ADS: LPHP and HPLP circuits

You need 4 VAR blocks: Input\_Parameters, Common\_calc, LCCL\_CLLC\_calcs, and either LCCL\_calcs or CLLC\_calcs

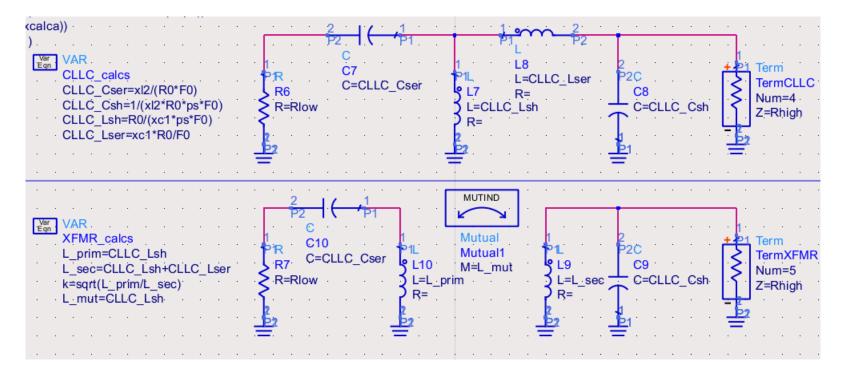

# The inductors in the CLLC topology can be replaced with a transformer.

These topologies are equivalent.

You need 5 VAR blocks: Input\_Parameters, Common\_calc, LCCL\_CLLC\_calcs, CLLC\_calcs, XFMX\_calcs

#### Compare the 4 networks

| LCLC_Csh1[1] | LCLC_Csh2[1] | LCLC_Lser1[1] | LCLC_Lser2[1] |

|--------------|--------------|---------------|---------------|

| 3.953400E-12 | 1.024265E-12 | 2.048529E-10  | 7.906801E-10  |

| CLCL_Cser1[1] | CLCL_Cser2[1] | CLCL_Lsh1[1] | CLCL_Lsh2[1] |

|---------------|---------------|--------------|--------------|

| 4.121705E-12  | 1.067870E-12  | 2.135739E-10 | 8.243409E-10 |

|               |               |              |              |

| LCCL_Cser[1] | LCCL_Csh[1]  | LCCL_Lser[1] | LCCL_Lsh[1]  |

|--------------|--------------|--------------|--------------|

| 1.328597E-12 | 3.177574E-12 | 1.873749E-10 | 9.012343E-10 |

|              |              |              |              |

| CLLC_Cser[1] | CLLC_Csh[1]  | CLLC_Lser[1] | CLLC_Lsh[1]  |

| 4.506171E-12 | 9.368743E-13 | 6.355149E-10 | 2.657194E-10 |

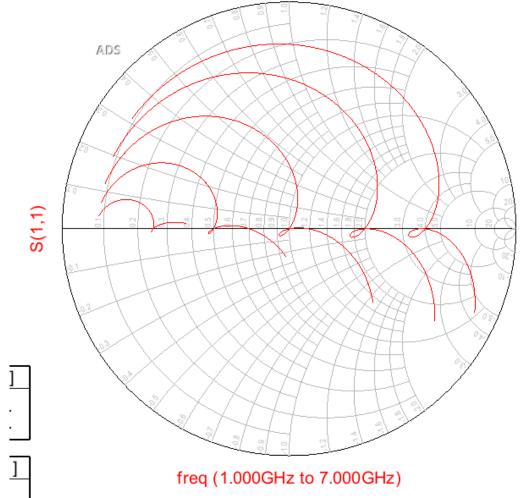

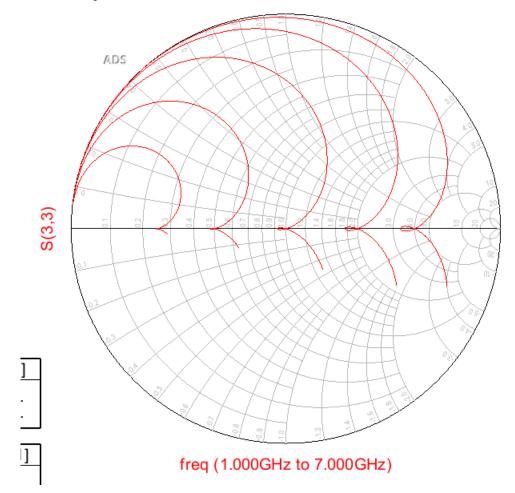

S11: LPLP (series L shunt C series L shunt C)S22: HPHP (series C shunt L series C shunt L)S33: LPHP (series L shunt C series C shunt L)S44: HPLP (series C shunt L series L shunt C, directly on top of S33)

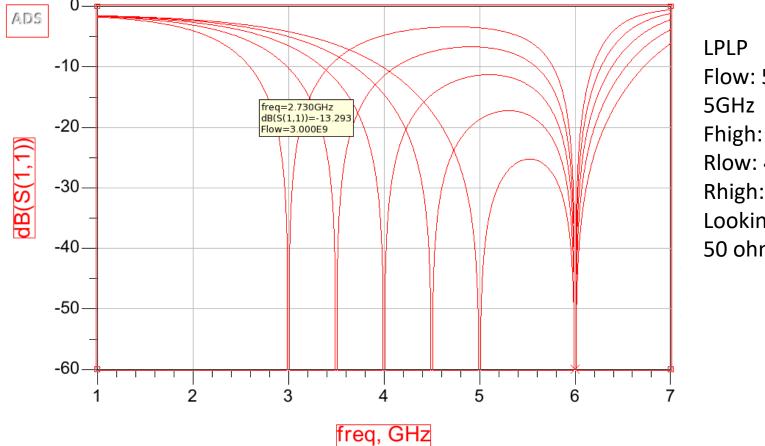

#### Sweep F\_low (F\_high is fixed)

Flow: 5 curves: 3-5GHz Fhigh: 6GHz Rlow: 4 ohms Rhigh: 50 ohms Looking at port 2, 50 ohm port.

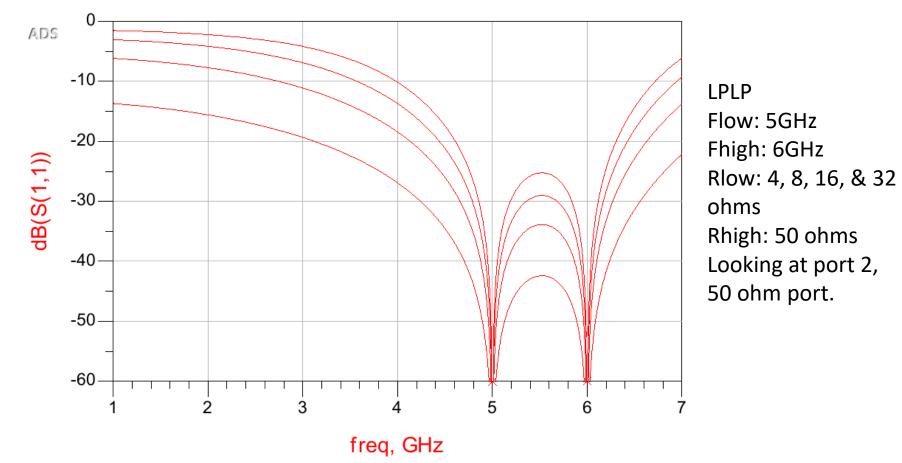

#### Sweep impedance ratio

#### Sweep Impedance Ratio

LPLP Flow: 5GHz Fhigh: 6GHz Rlow: 4 ohms Rhigh: 12.5, 25, 50, 100, 200 ohms Looking at port 2, 50 ohm port.

#### Sweep Impedance Ratio: LPHP

LPHP Flow: 5Ghz Fhigh: 6GHz Rlow: 4 ohms Rhigh: 12.5, 25, 50, 100, 200 ohms Looking at port 2, 50 ohm port.

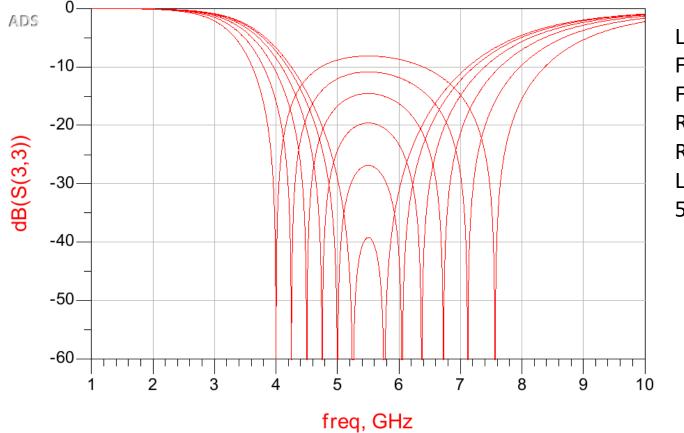

#### Vary BW with constant FO

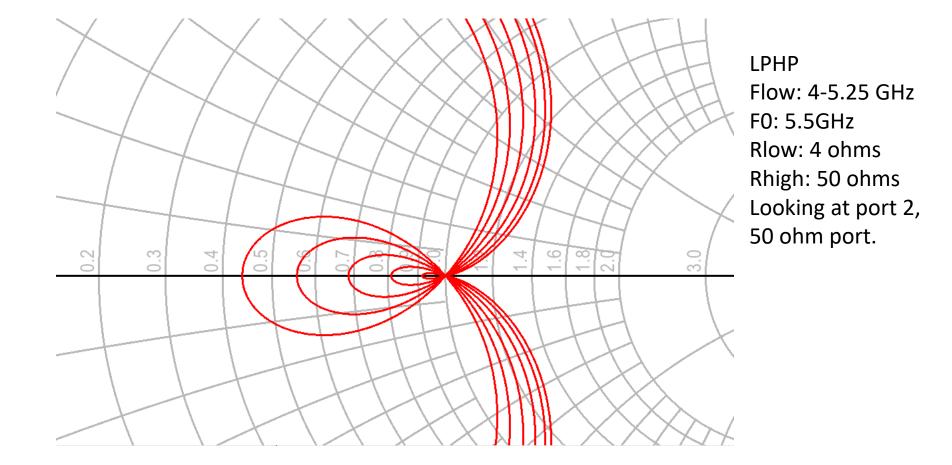

LPHP Flow: 4-5.25 GHz F0: 5.5GHz Rlow: 4 ohms Rhigh: 50 ohms Looking at port 2, 50 ohm port.

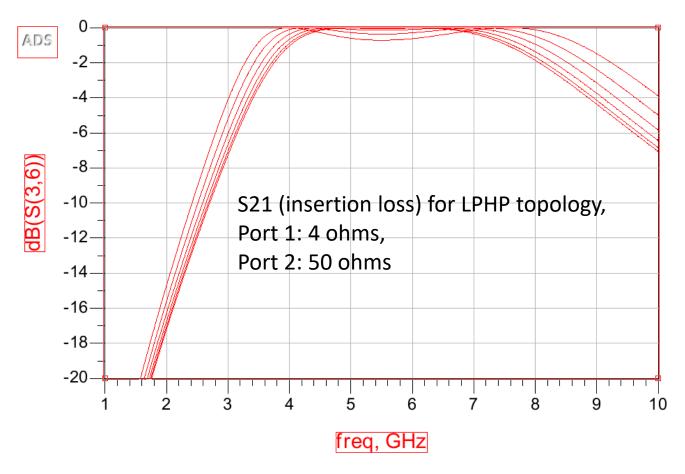

#### Vary BW with constant FO

LPHP Flow: 4-5.25 GHz F0: 5.5GHz Rlow: 4 ohms Rhigh: 50 ohms Looking at S21

#### Vary BW with constant FO

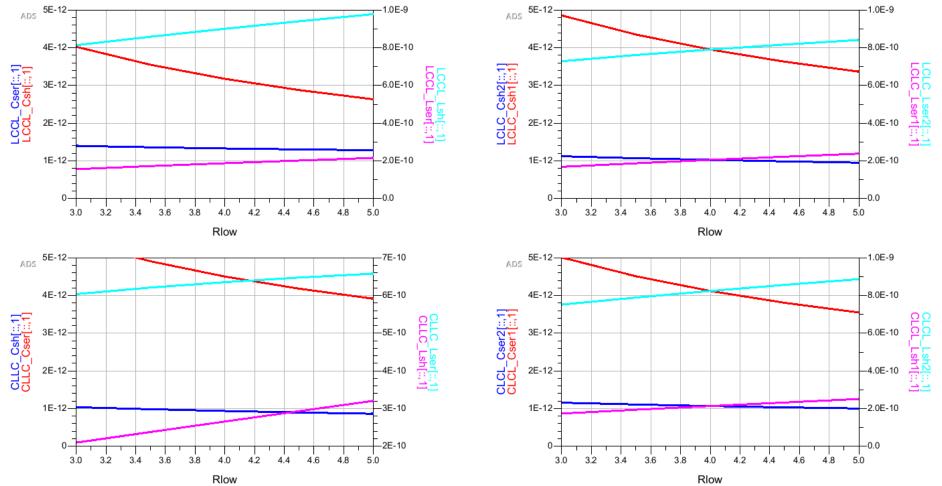

#### L,C Value vs. Design Goal

You can sweep a design goal (in this case, Rlow, which could be a load-line for a PA), keeping other design goals (BW, center freq, load R) constant, and see what component values are required to achieve this match, for the 4 topologies.

#### How do I get the actual element values in ADS?

- You specify the impedances, frequency, BW. How do you find out the component values?

- In ADS: go to your simulation controller: go to the "output" tab, click "add/remove", select the matching network(s), and the Csh1/Lser1 (etc., as appropriate, depending on whether you are using LPLP or HPHP). Variables will be exported to the display window.

- OR: Use the spread-sheet.

| 💭 📀 Scattering-Parameter Simulation:6 🚃 📀 🛛 🛞 |                                                                                                                                                                   |        |            |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|--|

| S_Param Instance Name                         |                                                                                                                                                                   |        |            |  |

| SP1                                           |                                                                                                                                                                   |        |            |  |

| Frequency                                     | Parameters                                                                                                                                                        | Noise  | Output 🛛 🔸 |  |

| Save by hier                                  | rarchy:                                                                                                                                                           |        |            |  |

|                                               |                                                                                                                                                                   | Maxim  | num Depth  |  |

| Measurer                                      | ment Equations                                                                                                                                                    | s: 2   |            |  |

| Save by nam                                   | ne:                                                                                                                                                               |        |            |  |

|                                               | Cser1<br>Cser2<br>Cshunt1<br>Cshunt2<br>Lser1<br>Lser2<br>Lshunt1<br>Cser1<br>Cser2<br>Cshunt1<br>Cser2<br>Cshunt1<br>Lser1<br>Lser2<br>Lser1<br>Lser2<br>Lshunt1 | ove    | •          |  |

| ок                                            | Apply                                                                                                                                                             | Cancel | Help       |  |

|                                               |                                                                                                                                                                   |        |            |  |

#### Implementation

- I have implemented this in a spread-sheet.

- I have also implemented this in ADS.

- Math is identical.

- Spread-sheet version: PerfectMatch\_v1

# Appendix

#### Overview

- A 4-element match can provide a nice fairly broad-band impedance match.

- Matching from low to high, we have 4 options:

- Series L Shunt C Series C Shunt L

- Series L Shunt C Series L Shunt C

- Series C Shunt L Series L Shunt C

- Series C Shunt L Series C Shunt L

- All have 4 variables.

- We have 4 design inputs: Frequency, Bandwidth, Impedance, Impedance transformation.

- 4 equations in 4 unknowns, it must be possible to make closed form equations to deduce the reactances required.

## Definitions

- Assume the input impedance is real and the output impedance is real. (If not, match out the imaginary part, and absorb that matching reactance into the matching network)

- Assume lossless components.

- Center Frequency is the geometric mean of the two nulls in S11 or S22.

- F0=SQRT(Flow \* Fhigh)

- Characteristic impedance (real) is the geometric mean of the input impedance and output impedance: Z=SQRT(Rlow \* Rhigh)

- Impedance transformation is Trans=sqrt(Rlow/Rhigh) (In this analysis, port 1 impedance is always lower than port 2, so Trans<1. If you want to go the other way, swap in and out.)

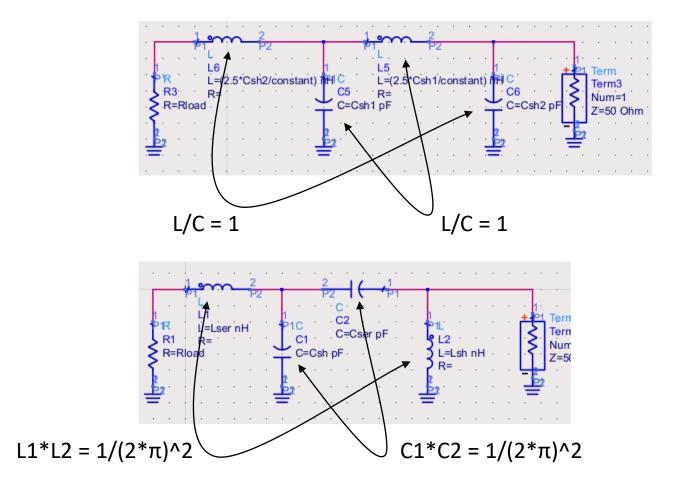

# Duality

- These networks are duals. Replace the capacitors with inductors of the same reactance, and replace the inductors with capacitors of the same reactance, and you get the same performance. (but shorts become opens, etc.)

- So, once you have one, the other is trivial to deduce.

# Duality

- These networks are duals. Replace the capacitors with inductors of the same reactance, and replace the inductors with capacitors of the same reactance, and you get the same performance. (but shorts become opens, etc.)

- So, once you have one, the other is trivial to deduce.

#### Scalability

- Center frequency is linearly scalable. Capacitance and inductance are inversely proportional to frequency.

- Characteristic impedance is linearly scalable. Capacitance is inversely proportional to characteristic impedance, inductance is proportional to characteristic impedance.

- So, all we need to do is design a matching network at F=1Hz, R0=1ohm, and we can scale up to any frequency and impedance.

- Bandwidth and transformation ratio are not obviously scalable.

## This is magic!

- There is an exact fixed ratio between elements in the matching networks. This ratio depends only on center frequency and characteristic impedance!

- As long as you obey this ratio, the impedance locus will go thru the middle of the Smith Chart.

For F0=1 R0=1

#### 4 equations for 4 unknowns

- So, we have 2 equations (last slide).

- Some simple algebra gives us a 3<sup>rd</sup> equation:

- For the LCLC case, (F0=1Hz, R0=1ohm)  $C_{sh2} = \frac{\sqrt{1-T^2}}{(2\pi)^2 C_{sh1}}$

- For the LCCL case, (F0=1Hz, R0=1hom)  $L_2 = C_1 + C_2$

- The final equation involves a quadratic, which, when solved, results in the two frequencies. However, that solution is itself a quadratic which is solved to yield the value of the capacitor as a function of T and the frequency spread. So, it involves the solution of nested quadratics. I'll spare the details.